Presentation partially realized at the Departamento de Ingeniería Eléctrica, Vicuña Mackenna 4860, Macul, Santiago, Pontificia Universidad Católica de Chile, on March 15th 2019

# Combined Effects of Ionizing Radiation and Electromagnetic Interference: The need of combined tests to achieve reliable systems

#### **FABIAN VARGAS**

ELECTRICAL ENGINEERING DEPT.

CATHOLIC UNIVERSITY - PUCRS

PORTO ALEGRE, BRAZIL

VARGAS@COMPUTER.ORG

Catholic University PUCRS

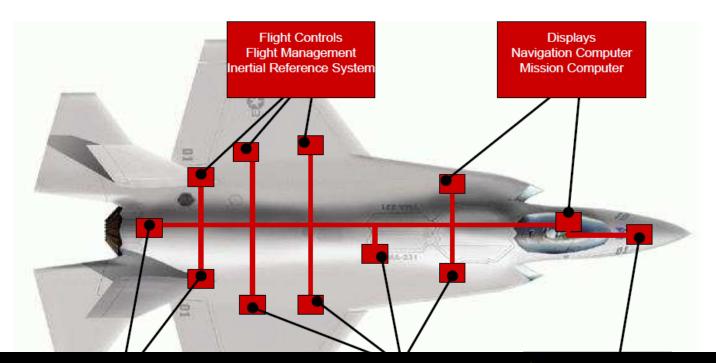

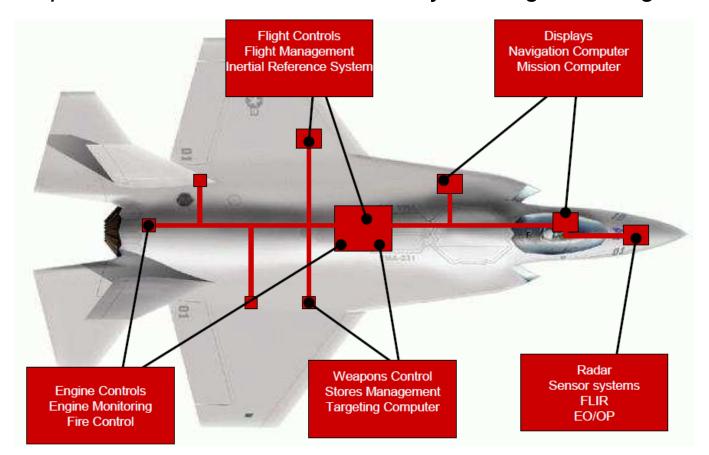

#### **Aerospace Industry**

**Designers** face a continuous pressure to use **new technologies** to improve **performance**, **cost** and **procurement time** for electronic systems devoted to **critical applications** (aerospace).

E.g., replace radiation-hardened ICs by COTS components!

#### **Aerospace Industry**

In avionics, most of the designs are moving from the **Federated Architecture: FA** (F-Control, F-Warning, Nav-System, Cabin Pressure, etc...)

FA approach: no longer feasible by the **continuous growing performance requirements** of modern aircrafts.

Reasons: huge **# of sub-systems** requires **unsustainable maintenance effort** as well as a tremendous budget requirements in terms of size, weight and power consumption (**SWaP**).

#### **Aerospace Industry**

to the **Centralized Architecture** (**IMA**: Integrated **M**odular **A**vionics) -> multiple functions with mixed criticality running on a single chip!

#### **Aerospace Industry**

These new architectures require the use of

fast and reliable ICs (such as NoC MPSoC-based systems,

FPGAs and memories) in mission-critical applications

which makes EMI & ionizing radiation control even

more challenging

#### **Current State-of-the-Art**

From the best of our knowledge ...

Only a few works addressing the problem: trying to understand and quantify the combined effects of ionizing (**total-ionizing dose: TID**) and non-ionizing (**EMI**) radiations on ICs

The Effects on Cardiac Pacemakers of Ionizing Radiation and Electromagnetic Interference from Radiotherapy Machines

(Int. Journal of Radiarion Oncology Biol. Phys. Vol. 4. pp. IO55-IO58, 1978)

**Pacemaker Failure Due to Radiation Therapy**

(PACE. Vol. 5, pp156-159, March-April 1982)

When cancer patients with implanted pacers undergo radiation therapy it is important to known whether the treatment will have any deleterious effects on the pacer, thus placing the patient in jeopardy from malfunction. Malfunction may consist of continuous or intermittent spurious signals or an interruption of normal pacer signals.

Radiation therapy exposes a pacemaker to ionizing radiation alone (60Co), or ionizing radiation plus strong electromagnetic fields (linear accelerators and betatrons), which may induce noise and interference into reactive electronic circuits.

#### **Current State-of-the-Art**

From the best of our knowledge ...

Electromagnetic Interference and Ionizing Radiation Effects on CMOS Devices (IEEE TRANS. ON PLASMA SCIENCE, VOL. 40, NO. 6, JUNE 2012)

N- and PMOS devices presented shift and distortion of the voltage and current transfer characteristics, leading to reduced noise margins and logic instability.

"EMI + TID combination proved most damaging, when compared to isolated EMI and ionizing radiation experiments"

None work, except from our group, focused on the combined effects of ionizing (**soft errors in memory elements**) and non-ionizing (**EMI**) radiations on ICs

#### **Current State-of-the-Art**

From the best of our knowledge ...

#### Absence of a **standard** to rule combined tests

(currently, only a Draft Recommendation from ITU: "Overview of particle radiation effects on telecommunications systems", Geneva, Oct. 2016)

Our studies have shown a **considerable reliability degradation** for systems operating in harsh environments (such as space, where satellite electronics is exposed to the combined effects of ioninzing rad: TID/soft errors and EMI)

(Analysis of SRAM-Based FPGA SEU Sensitivity to Combined EMI and TID-Imprinted Effects, IEEE TRANS. ON NUCLEAR SCIENCE, VOL. 63, JUNE 2016)

### Where is the problem?

It is a common practice that ...

engineers qualify electronic systems to EMI, TID or SEU, or eventually to all of them, but often NOT taking into account the combined effects one phenomenon may take over the other.

e.g., assume a given part of an embedded system for satellite application is certified by a set of EMI tests according to specific stds

### Where is the problem?

After a given period of time

Who can ensure that this pull vill still perforn same set of EMI stds, after a given level cumulated over time on the system, if the for EMI and radiation?

radiation has been certified independently

Moreover, who can ensure that the same will be approved for the same set of EMI stds, if operating in a hereh environment with dense flux of high-energy particles (SEEs)?

### How to test/qualify such electronics?

In the light of this problem ...

We ...

- analyze the impact of combined tests for EMI

- + radiation (TID/SEU) on the reliability of electronic components

- propose a new methodology that takes this combination into account in order to qualify state-of-the-art COTS ICs

### **Outline**

- 1. Understand the effects of ionizing radiation (TID, SEU, SEE) & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

#### Types of radiation: *lonizing* X *Non-lonizing* ...

**Non-ionizing radiation** refers to any type of electromagnetic radiation that does not carry enough energy to remove an electron from an atom or molecule. Thus, it has energy only to excite an electron to a higher energy state

On the other hand, **ionizing radiation changes** the matter characteristics when passing through it by producing **charged ions**

|            |            | Non-io      | nizing    |              |        | lonizing |     |

|------------|------------|-------------|-----------|--------------|--------|----------|-----|

| Wavelength | 100,000 km | 1 mm        | 700 mm    | 380 nm       | 10 nm  | 0.01 nm  |     |

| Frequency  | 3 Hz       | 300 GHz     | 430 THz   | 790 THz      | 30 PHz | 30 EHz   |     |

|            |            | Radio Infra | ared Visi | ible Ultravi | olet   | X-ray Ga | mma |

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE)

- & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

# Understanding the Effects of Radiation on Electronics

Mechanisms of radiation interaction can cause a wide variety of changes in circuit & systems' performance

The observed degree of chance depends on the device type and radiation type

It is useful to treat the mechanisms of radiation interaction in terms of <a href="Iong duration">Iong duration</a> and <a href="Iong duration">transient effects</a>

**Total Ionizing Dose (TID)**

**Single-Event Effects (SEEs)**

Single-Event Upset (SEU)

**Single-Event Transient (SET)**

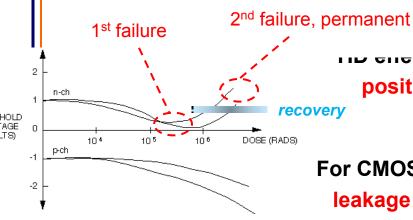

# Understanding the Effects of Radiation (TID) on Electronics

For critical applications (military, aerospace or biomedical) reliability assurance to total ionizing dose (TID) radiation is always at a premium being a key-issue for the success of such products in the market.

יוו בווכינts on CMOS ICs are caused primarily by positive charge trapped in insulating layers

For CMOS ICs, the main TID effect is the increase of leakage currents and change in  $V_{th}$  of the devices

For high doses, a permanent functional failure of the circuit is observed.

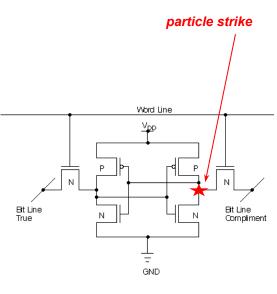

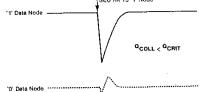

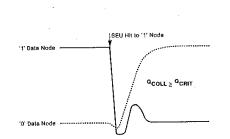

### **Understanding the Effects of** Radiation (SEE) on Electronics

Radiation (SEU) effects on CMOS ICs are mainly caused by high-energy particles striking reverse biased drain depletion region of off-transistors

For CMOS ICs, the main SEU effect is the loss of information stored in memory elements (FFs, RAMs)

Transient functional failure of the circuit is observed

#### particle strike

Fig. 1. Illustration of the charge collection mechanism that cause single-event upset: (a) particle strike and charge generation; (b) current pulse shape generated in the n+p junction during the collection of the charge.

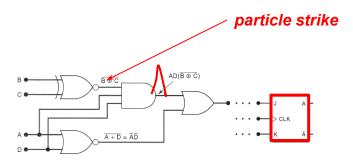

# Understanding the Effects of Radiation (SEE) on Electronics

Radiation (SET) effects on CMOS ICs are mainly caused by high-energy particles striking logic along with critical paths

For CMOS ICs, the main <u>SET</u> effect is the loss of information stored in memory elements (FFs, RAMs)

Transient functional failure of the circuit is observed

### **Radiation Testing Standards**

#### **USA Department of Defense**

1034

#### Test Procedure of MIL-STD-883H - Test Method for Microcircuits

| METHOD NO.                                                                | ENVIRONMENTAL TESTS                               |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| 1001                                                                      | Barometric pressure, reduced (altitude operation) |  |  |  |  |

| 1002                                                                      | Immersion                                         |  |  |  |  |

| 1003                                                                      | Insulation resistance                             |  |  |  |  |

| 1004.7 Moisture r                                                         | resistance                                        |  |  |  |  |

| 1005.8Steady sta                                                          | ate life                                          |  |  |  |  |

| 1006                                                                      | Intermittent life                                 |  |  |  |  |

| 1007                                                                      | Agree life                                        |  |  |  |  |

| 1008.2Stabilization                                                       | on bake                                           |  |  |  |  |

| 1009.8 Salt atmos                                                         | sphere (corrosion)                                |  |  |  |  |

| 1010.7Temperature cycling                                                 |                                                   |  |  |  |  |

| 1011.9Thermal s                                                           | hock                                              |  |  |  |  |

| 1012.1Thermal c                                                           | haracteristics                                    |  |  |  |  |

| 1013                                                                      | Dew point                                         |  |  |  |  |

| 1014.10                                                                   | Seal                                              |  |  |  |  |

| 1015.9Burn-in te                                                          |                                                   |  |  |  |  |

| 1016                                                                      | Life/reliability characterization tests           |  |  |  |  |

| 1017.2 Neutron in                                                         |                                                   |  |  |  |  |

|                                                                           | ater-vapor content                                |  |  |  |  |

|                                                                           | adiation (total dose) test procedure              |  |  |  |  |

|                                                                           | induced latchup test procedure                    |  |  |  |  |

| 1021.2Dose rate upset testing of digital microcircuits                    |                                                   |  |  |  |  |

| 1022                                                                      | Mosfet threshold voltage                          |  |  |  |  |

|                                                                           | response of linear microcircuits                  |  |  |  |  |

| 1030.1 Preseal bu                                                         |                                                   |  |  |  |  |

| 1031                                                                      | Thin film corrosion test                          |  |  |  |  |

| 1032.1 Package induced soft error test procedure (due to alpha particles) |                                                   |  |  |  |  |

| 1033                                                                      | Endurance life test                               |  |  |  |  |

Die penetrant test (for plastic devices)

### **Radiation Testing Standards**

# **European Space Agency Agence Spaciale Européenne**

TOTAL DOSE STEADY-STATE IRRADIATION

**TEST METHOD**

ESA/SCC BASIC SPECIFICATION No. 22900

SINGLE EVENT EFFECTS TEST METHOD

AND GUIDELINES

ESA/SCC Basic Specification No. 25100

space components coordination group

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE)

- & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

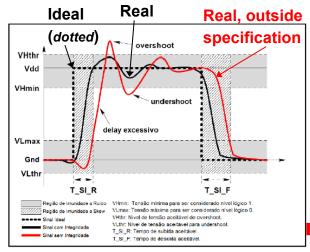

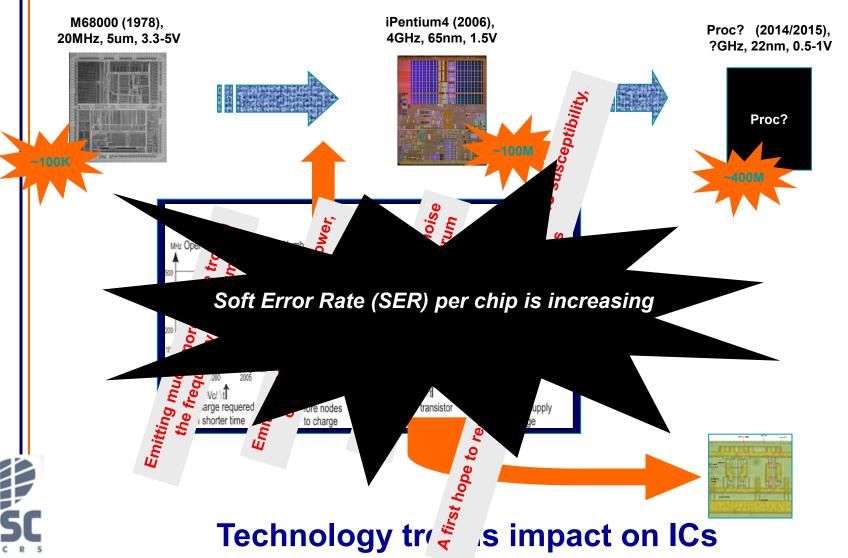

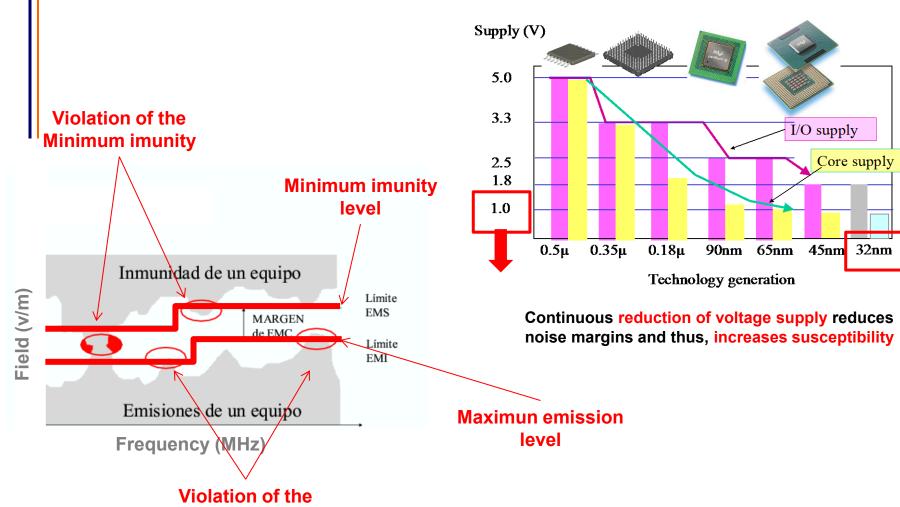

# Understanding the Effects of EMI on Electronics

The increasing hostility of the electromagnetic environment caused by the widespread adoption of electronics, (mainly wireless technologies), represents a huge challenge for the reliability of RT embedded systems.

**Electromagnetic Interference (EMI)**

**Power Supply Disturbances (PSD)**

**Transient Faults**

Signals outside noise margins can be erroneously interpreted and stored by memory elements at the end of critical paths

# Understanding the Effects of EMI on Electronics

# Understanding the Effects of EMI on Electronics

**Maximun emission**

#### **IEC International Standards**

IEC 61.000-4-17: Electromagnetic compatibility (EMC) – Part 4-17: Testing and measurement techniques – Ripple on d.c. input power port immunity test.

IEC 61.000-4-29: Electromagnetic compatibility (EMC) – Part 4-29: Testing and measurement techniques – Voltage dips, short interruptions and voltage variations on d.c. input power port immunity tests".

IEC 62.132: Measurements of Electromagnetic Immunity, 150 kHz – 1 GHz:

Part 1: General conditions and definitions

Part 2: (G-) TEM Cell Method

Part 3: Bulk Current Injection (BCI) Method

Part 4: Direct RF Power Injection Method

Part 5: Workbench Faraday Cage Method

Radiated Method

**Conducted Methods**

These IEC stds are limited to 1 GHz. The demand for extended frequency range validity has motivated ongoing research on more accurate tests.

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE) & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

### Existing Techniques to Protect Against (TID) Radiation

- Use of guardbands: slow down clock frenquency, put extra timing margins

- Prefer use of modern technologies (insead of old, mature ones): scaling down is always a good option since nanotechnologies (typically under 65nm) are strongly TID-tolerant

- Use of TID-tolerant std cells library (build-up pMOS devices much larger than nMOS devices, replace NOR gates by Nand ones, etc ....)

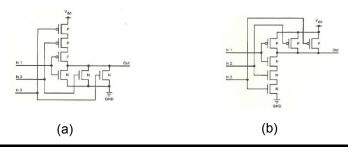

CMOS circuit schematic: (a) NOR gate; (b) NAND gate:

NAND gate has shown in Co<sup>60</sup> tests to retain a higher degree of its original noise margins with radiation and is thus the preferred logic gate for hardened IC designs.

# Existing Techniques to Protect Against (SEU) Radiation

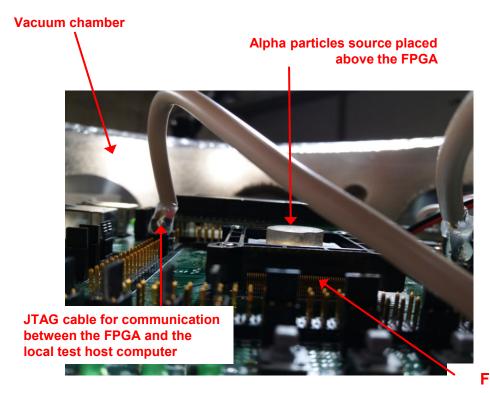

- Use of HW, SW, Time & Information (EDAC) Redundancy such as TMR, Functional Units Duplication with Comparator, Interleaving, etc ...

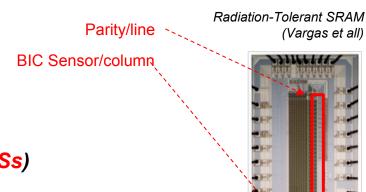

- Use of Build-In Current Sensors (BICSs)

### Existing Techniques to Protect Against (SEU) Radiation

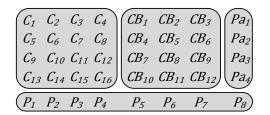

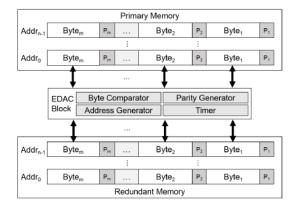

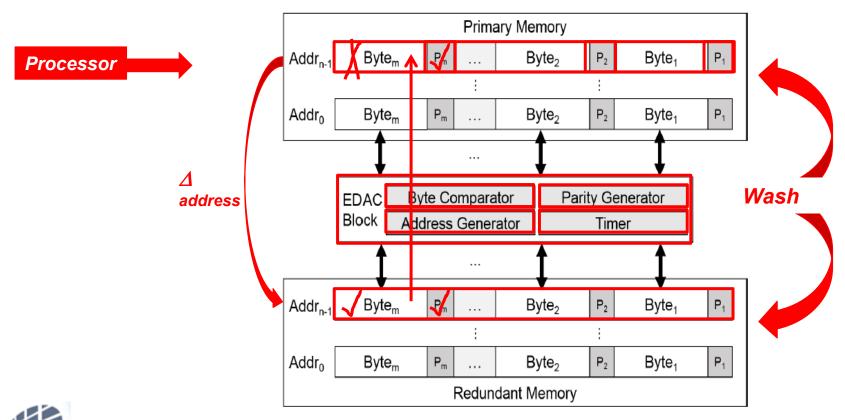

- EDAC in Memory Array: Parity, Hamming Extended, Checksum, CRC, Reed-Muller, Matrix, CLC, ...

**Codified CLC word model**

Parity-per-Byte and Duplication (PBD) Approach

# Existing Techniques to Protect Against (SEU) Radiation

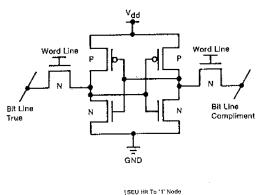

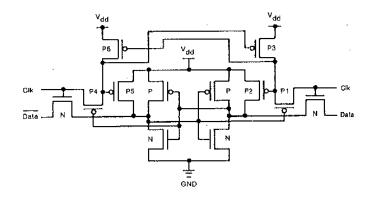

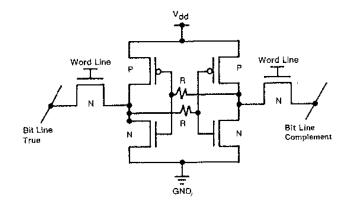

- Use of SEU-tolerant std cells library: design rad-hard SRAM cells

Classic CMOS SRAM cell schematic and the critical charge ( $Q_{crit}$ ):

#### Design-hardened CMOS SRAM cell schematics:

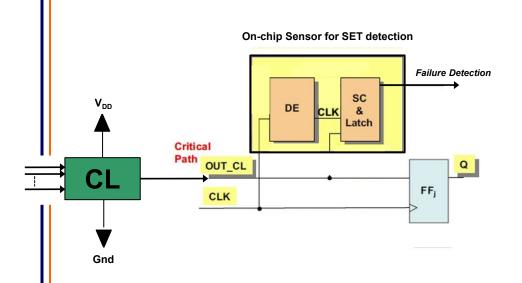

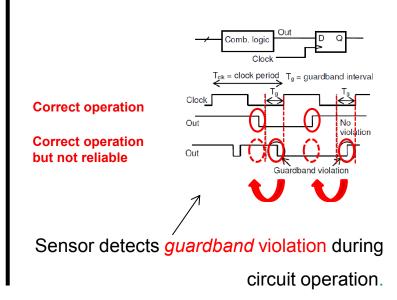

# Existing Techniques to Protect Against (SET) Radiation (also valid for EMI, TID, Aging)

- Use of on-chip sensors at the output of critical paths to detect the occurrence of single-event transients (i.e., an unwanted glitch captured by a FF at the path output.

This approach is quite similar to the addition of on-chip aging sensors to predict circuit aging and then, recovery before failure occurrence.

According to the degree of perturbation detected by the sensor, it increases the  $V_{DD}$  source.

Can be implemented in FPGA or custon IC.

**Process repeated** till the end of the circuit lifetime.

# Existing Techniques to Protect Against (SET) Radiation (also valid for EMI, TID, Aging)

#### **Developed Technique:**

"Detection of aging in a Combinational Circuit by Slack Measurement in FPGA"

Poof of Concept on a Xilinx Zynq z7000 (Part N. XC7Z010-1CLG400C)

# Existing Techniques to Protect Against (SET) Radiation (also valid for EMI, TID, Aging)

#### Detection of aging in a Combinational Circuit by Slack Measurement in FPGA (proof of concept)

Circuit Aging Detection Based on Time Slack Measurement: a concept validation in FPGA

Jardel Silveira, Jarbas Silveira, Caio Amaral, Fabian Vargas

Federal University of Ceara

Pontifical Catholic University of Rio Grande do Sul

#### **Existing Techniques to Protect Against EMI...**

#### Increasing immunity to power supply fluctuations:

- On-chip decoupling "power supply / core" (near I/O ports):

- (a) minimize transient currents and voltage swings (mainly on substrate, reducing Gnd bounce) and

- (b) prevent external noise from entering power pins

#### **Existing Techniques to Protect Against EMI...**

#### Increasing immunity to power supply fluctuations:

- <u>Perform a dedicated power distribution design by means of</u>

<u>multiple paths</u> to drive large amounts of current induced by fast logic switching activity ⇒ <u>minimizes V<sub>DD</sub>/Gnd bounce</u>

- <u>Design circuits to work within low operating frequency rates</u>: <u>use of guardbands to increase noise margins</u>

- <u>Design of asynchronous logic</u> by migrating existing clocked architectures or designing new ones ⇒ <u>intrinsically delay-insensitive</u>

DLX Processor (ASPIDA Project - Asynchronous Open-Source Ip of the DIx Architecture) (http://www.ics.forth.gr/carv/async/demo/)

Asynchronous Circuits and Systems Group of Institute of Computer Science – FORTH, University of Crete, and Microelectronics Group of Politecnico di Torino

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE) & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

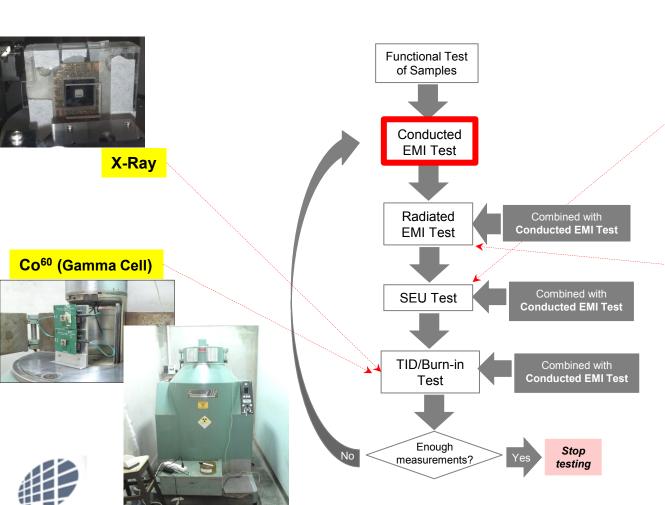

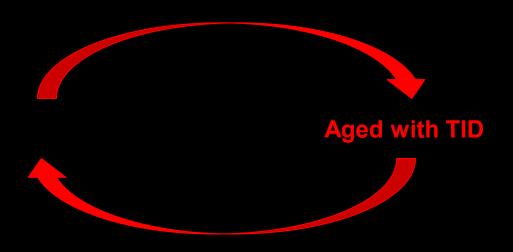

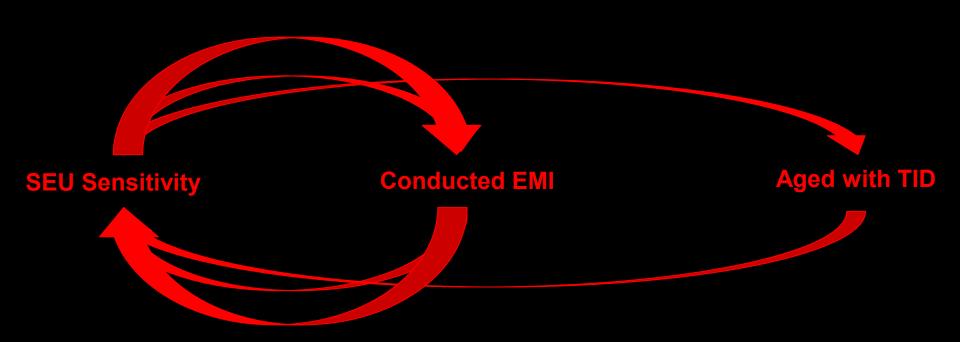

## **Combined Test Planning Methodology**

Combined tests: *EMI* + *Radiation*

SEU

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE) & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

## Goal

### In this context...

We have been developing a configurable platform suitable for combined tests of EMI, radiation and aging measurements of prototype embedded systems

- The platform can be used to perform measurements on ICs and embedded systems having in mind EMI and radiation international stds:

- IEC 62.132-2 (for radiated EMI noise)

- IEC 61.0004-17 and IEC 61.0004-29 (for conducted EMI noise)

- TID: 1019.4 & 1032.1 methods for (TID & SEU Test Procedures of MIL-STD-883H)

16MB SRAM (RTOS

user application)

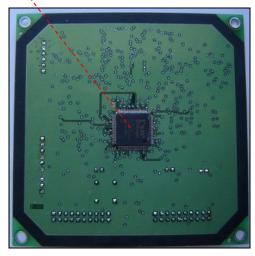

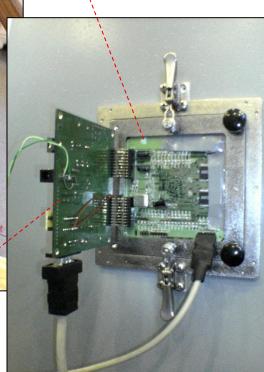

### Platform (HW parts)

FPGA (System-on-Chip)

### **System under Test**

Top view

**Bottom view**

IEC 62.132-2 std compliant board.

Four-layers: Gnd (top) - signal - signal - Vdd (botton).

**Interface Board**

Top (test side)

**Bottom (glue logic)**

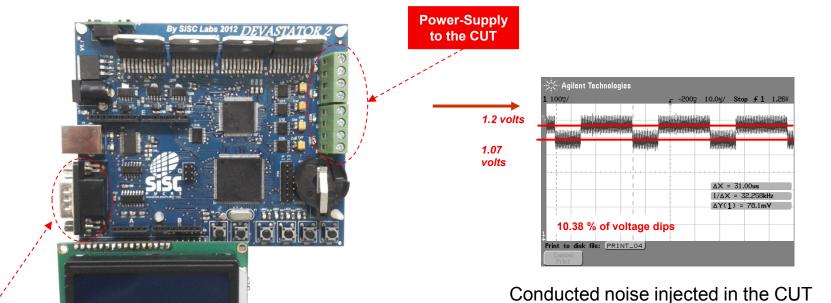

### IEC 61.000-4-17 and -29 Compliant External EMI Noise Injector

Configurable

from PC (Serial port)

| Test<br>Type | Level | Percentage of the<br>nominal DC<br>voltage |

|--------------|-------|--------------------------------------------|

| Ripple       | 1     | 2                                          |

|              | 2     | 5                                          |

|              | 3     | 10                                         |

|              | 4     | 15                                         |

|              | X     | X                                          |

| Test<br>Type | Test Level (%) | Duration<br>(s) |

|--------------|----------------|-----------------|

| Voltage      | 40, 70 or X    | 0.01            |

| Dips         |                | 0.03            |

|              |                | 0.1             |

|              |                | 0.3             |

|              |                | 1               |

|              |                | X               |

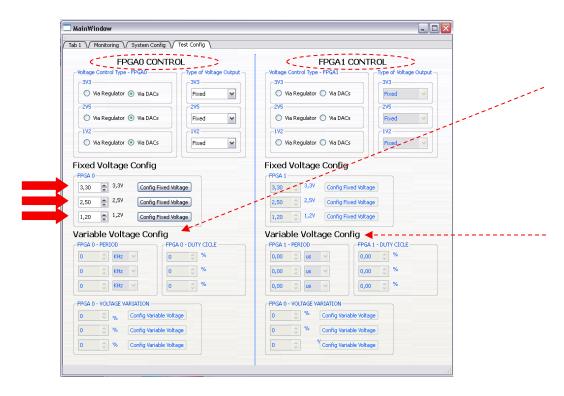

### **Programming interface of the platform:**

Screenshot of the configuration environment to perform tests according to the IEC stds 61.000-4-17 and 61.000-4-29

### **Laboratory Setup**

Microsemi ProAsic3E1500

### Goal:

### **SEU** sensitivity w.r.t. V<sub>DD</sub> Disruption and TID

- 1. Understanding the effects of ionizing radiation (TID, SEU, SEE) & non-ionizing radiation (EMI) on embedded electronics

- 2. Mitigation techniques

- 3. Combined test planning

- 4. Configurable platform and lab requirements for combined test

- 5. Experiments combining TID + SEU + EMI tests on FPGAs

# Combined Tests: Conducted EMI with TID

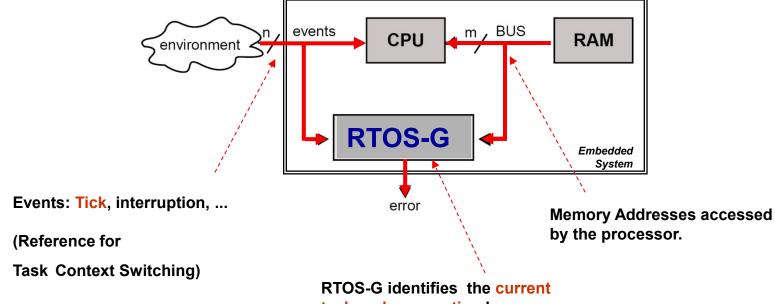

IP Core: RTOS-Guardian (RTOS-G), a watchdog to monitor RTOS activity in embedded systems

the RTOS-G targets faults that ESCAPE detection by the native structures present in the RTOS kernel.

RTOS-G identifies the current task under execution by correlating addresses flowing through the bus with the information stored in an Address Table generated during the compilation process.

Block diagram of the target embedded system

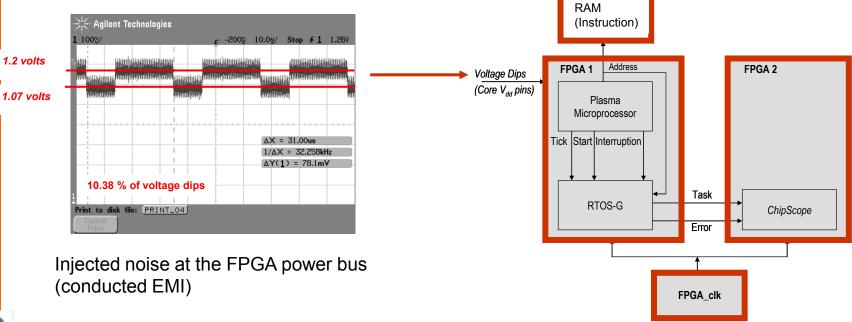

Fault injection campaign: generated according to the IEC 61.000-4-29 Int. Std. for conducted EMI on the DC input power port of (fresh) FPGA 1

**Voltage dips** were randomly injected at the **FPGA 1**  $V_{dd}$  input pins at a frequency of **25.68 kHz** and consisted of dips of about **10.83% of the nominal**  $V_{dd}$ .

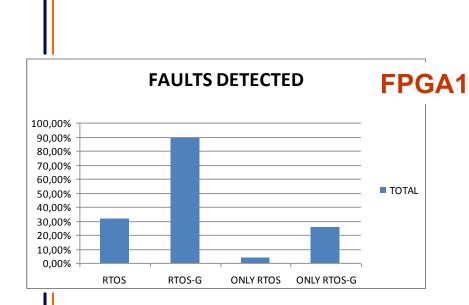

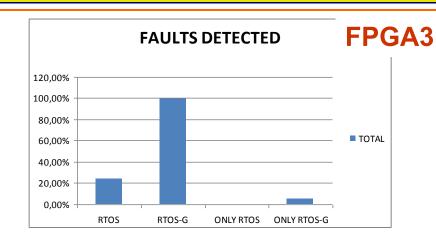

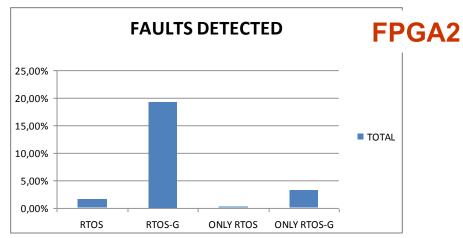

### **Results for Fault Detection**

As long as more complex services of the kernel are used, the higher is the RTOS error detection.

The native fault detection mechanism (assert() function) is called by the kernel every time RTOS runs its services (message queues, semaphores).

| Benchmark | RTOS Kemel [%] | RTOS-G [%] |

|-----------|----------------|------------|

| BMI       | 2.40           | 99.90      |

| BM2       | 25.90          | 100.00     |

| BM3       | 45.80          | 100.00     |

| Average   | 24.70          | 99.97      |

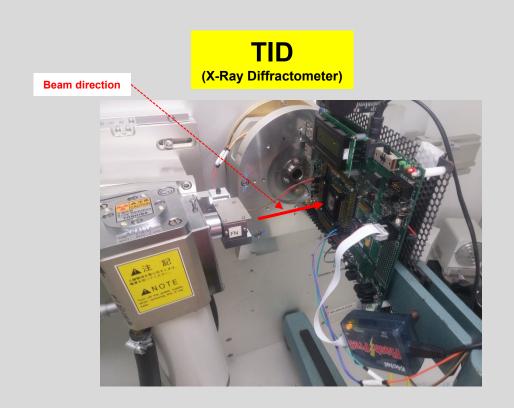

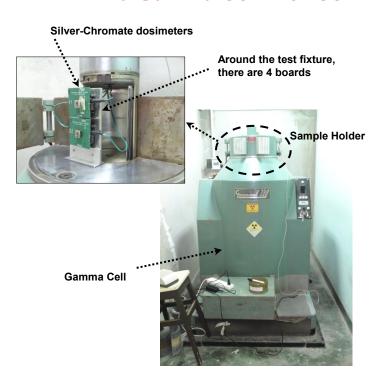

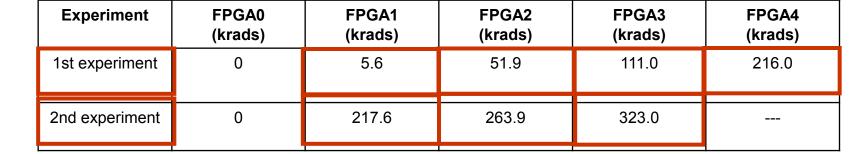

### Fault injection campaign: TID irradiation of FPGA1

in a Gamma Cell with Co60

RTOS-G: 68,67%

RTOS: 18,00%

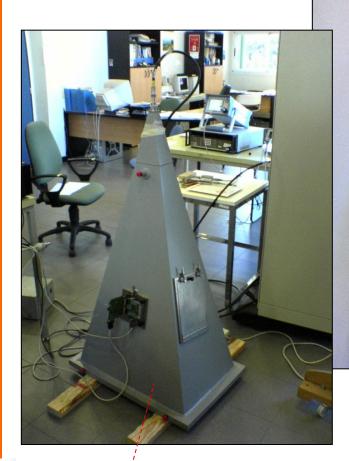

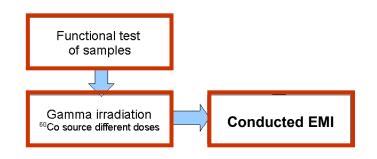

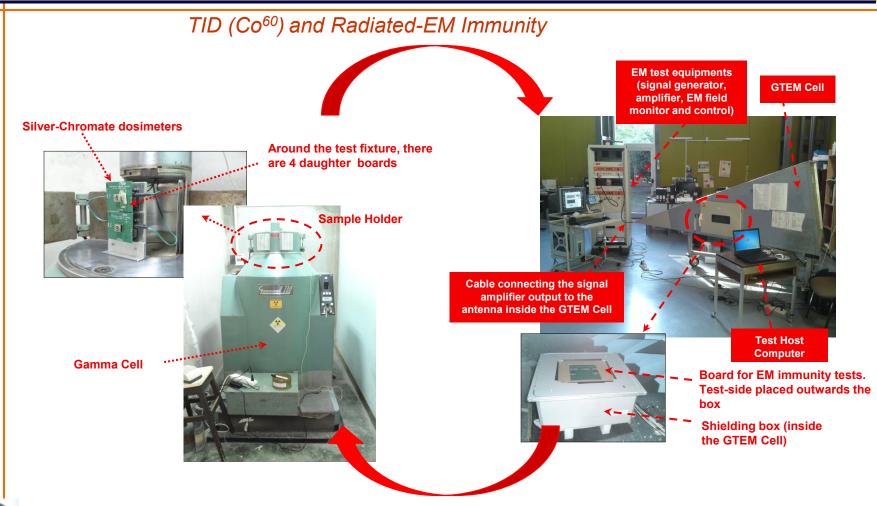

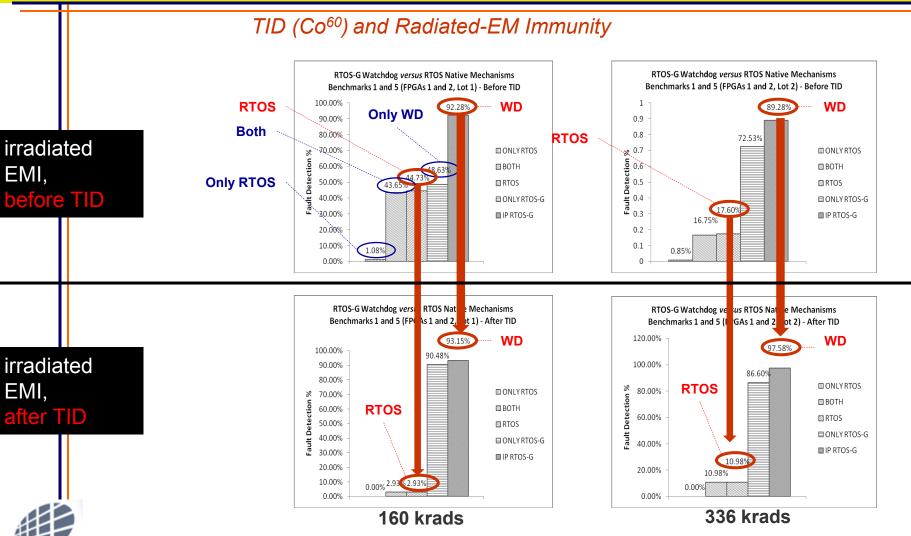

# Combined Tests: Radiated EMI with TID

### Combined tests:

### TID (Co<sup>60</sup>) and Radiated-EM Immunity

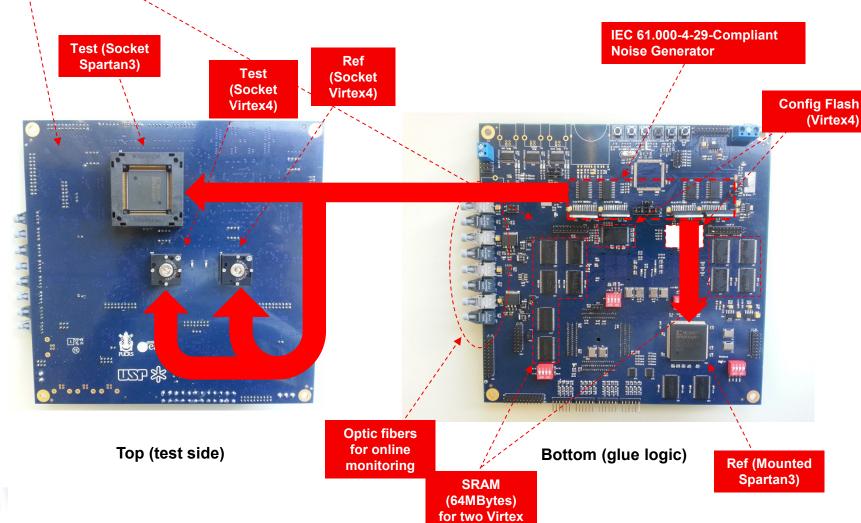

1st Part\*: 4 fresh FPGAs Virtex4 (XC4VFX12-10SF363) were characterized to radiated EM Immunity.

\* based on IEC 61.132-2 Std (TEM Cell Method).

### Test method conditions:

- EM field range: from 10 to 120 v/m (volts/meter);

- Radiated signal frequency range: [150kHz 1GHz];

- Signal modulation: AM Carrier 80% modulation at 1kHz, Horizontal Polarization.

2<sup>nd</sup> Part\*\*: aging by TID exposition:

- Fab. Lot 1: 2 FPGAs received a total dose of 160 krads

- Fab. Lot 2: 2 FPGAs received a total dose of 336 krads

<sup>\*\*</sup> based to MIL-883H Std (1019.8 Method for TID radiation testing), room temperature, dose rate: 155.5 rads/s.

### **Combined tests:**

Radiation source used for gamma radiations.

Environment for radiated EM immunity measurements.

### Combined tests:

Comparison between the fault detection capability of the WD against the RTOS native fault detection mechanisms for fresh and aged FPGAs operating in an EMI-exposed environment

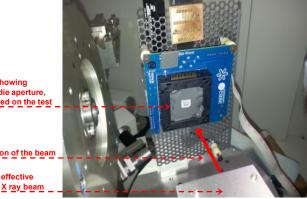

# Combined Tests: Conducted EMI with TID and SEU

### Goal:

### SEU sensitivity as a function of V<sub>DD</sub> Disruption and TID

**TID** (X-Ray Diffractometer)

**DUT** showing open-die aperture,

Direction of the beam

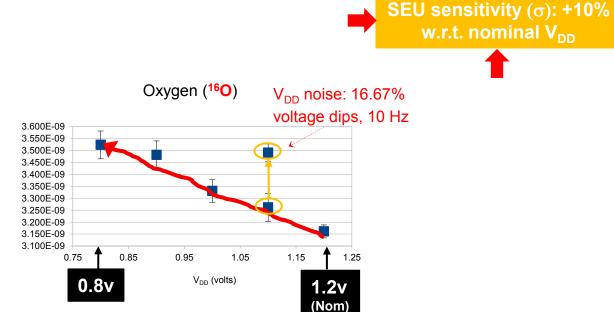

(<u>Configuration Bitstream</u>) SEU sensitivity as function of Noise on Power Supply (V<sub>DD</sub>) (**Fresh FPGA**)

SEU sensitivity (σ): +11% w.r.t. nominal V<sub>DD</sub>

### Xilinx Spartan3 XC3S500E

### **Experiment (3)**

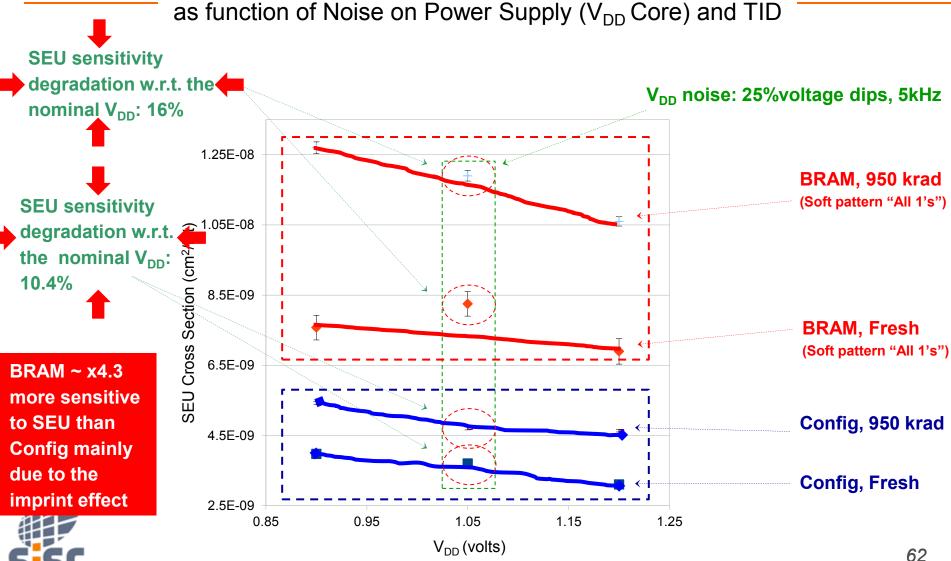

(BRAM vs. Config) SEU sensitivity as function of Noise on Power Supply (V<sub>DD</sub> Core) and TID

PS: TID deposited with all BRAM cells storing "0s" (the hard pattern)

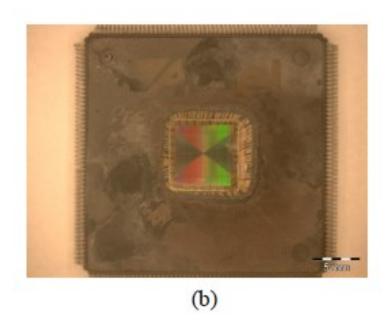

# Combined Tests: Conducted EMI with SEU

### Parity per Byte & Duplication (PBD) EDAC Technique

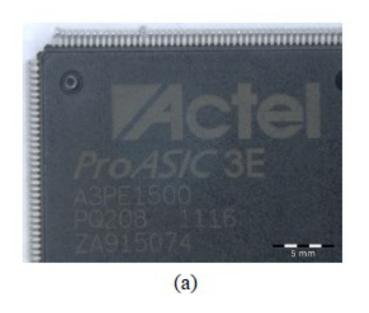

### Microsemi ProAsic3E A3PE1500 FPGA:

- (a) Packaged device;

- (b) Unpacked, ready for radiation (SEU and TID) tests.

### **SEU Test:**

ProASIC3E FPGA exposed to 5.4 MeV alpha particles emitted by a <sup>241</sup>Am source

Alpha-particle flux:. Appr. 1,300 part/cm<sup>2</sup>.s

(13.7 particles/second /millisteradian)

Test setup for the <sup>241</sup>Am source

FPGA under test

# Combined Test for SEU/Conducted EMI

### PROASIC3E OCCUPIED RESOURCES

| FPGA Hardware<br>Summary       | Core Logic<br>(VersaTiles) | FFs    | SRAM<br>Cells |

|--------------------------------|----------------------------|--------|---------------|

| Used hardware<br>configuration | 37,903                     | 18,432 | 276,480       |

| Max. hardware<br>available     | 38,400                     | 38,400 | 276,480       |

|                                |                            | ,      | ↓<br>100%     |

|                                | √<br>48%                   |        |               |

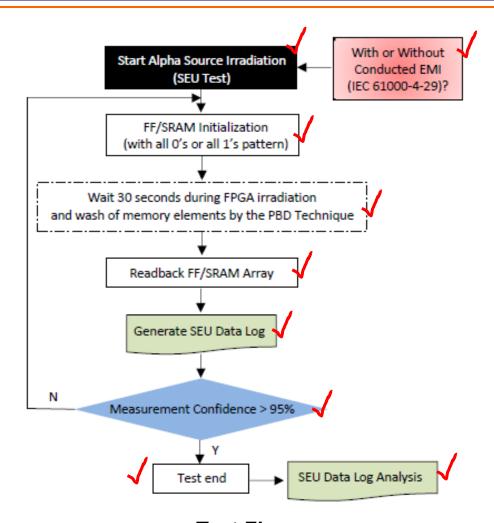

**Test Flow**

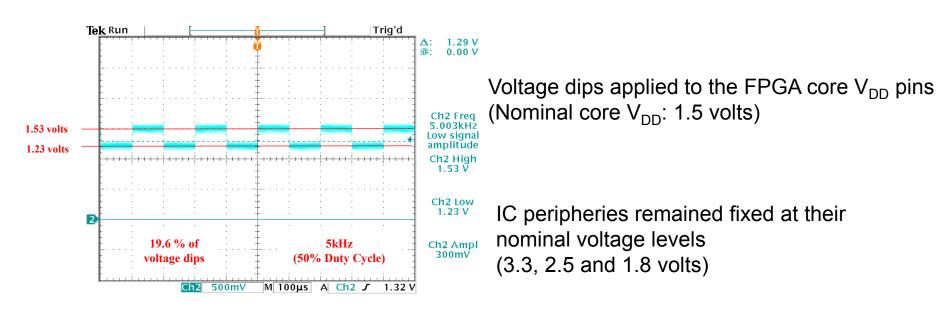

### **EMI Test:**

Fault injection campaigns were generated according to the IEC 61000-4-29 Std

**Fig. 6.** Noise injected on FPGA V<sub>DD</sub> pins.

### **Obtained Results**

### TABLE II.

CAPABILITY OF THE PBD TECHNIQUE TO MITIGATE SOFT ERRORS INDUCED BY ALPHA PARTICLES, WITH AND WITHOUT CONDUCTED EMI NOISE ON THE CORE INPUT POWER PORT OF THE FPGA.

RESULTS FOR THE SRAM ARRAY.

| PBD Technique Effectiveness to Alpha Particles, with and without conducted EMI noise on input power port |                  |               |                        |  |  |

|----------------------------------------------------------------------------------------------------------|------------------|---------------|------------------------|--|--|

| Average number of                                                                                        | Without<br>Noise | With<br>Noise | Soft Error<br>Increase |  |  |

| observed bit-flips                                                                                       | 395.00           | 1,049.00      | 2.7                    |  |  |

| bit-flips per memory bits                                                                                | 0.0027           | 0.0071        | 2.6                    |  |  |

| bit-flips per second                                                                                     | 0.4760           | 1.0708        | 2.3                    |  |  |

| bit-flips per memory bits per<br>second                                                                  | 0.0028           | 0.0073        | 2.6                    |  |  |

| addresses corrected**                                                                                    | 393.33           | 1,044.37      | 2.7                    |  |  |

| addresses not corrected                                                                                  | 0.17             | 0.63          | 3.7                    |  |  |

| masked addresses***                                                                                      | 0                | 0             | 0                      |  |  |

| EDAC Effectiveness (%)                                                                                   | 99.96            | 99.94         |                        |  |  |

<sup>\*&</sup>quot;Soft Error Increase" rate computed as: With Noise/Without Noise.

<sup>\*\*</sup>the number of addresses corrected is smaller than the number of observed bit-flips because there was at least one address with more than one bit flip.

<sup>\*\*\*</sup>masked addresses are addresses not detected and not corrected, thus escaping detection by the proposed technique.

### **Obtained Results**

Compared to only ionizing radiation, when the IC was additionally exposed to conducted EMI, FF & SRAM arrays became

~ 2.7 times more sensitive to soft errors

# We can compute the required ∆t (wash time interval) for a given expected mean-time before failure (MTBF):

MTBF: in order to calculate a conservative MTBF we assume the system lifetime should be 10 times greater than the lifetime desired for the target system.

If a system lifetime of 15 years is desired, then a reasonable MTBF of 150 years (**5.475x10**<sup>4</sup> **days**) is assumed.

Assume also that the FF and SRAM arrays store a relative sensitive data for which we could not accept more than **5 errors** over the whole mission time.

Therefore, the target **MTBF** = **10,950** days  $(5.475 \times 10^4/5)$

### **FPGA Parameters:**

- a) Word size: 16 bits (+ 2 parity bits) = 18 bits

- b) SRAM capacity: 276,480 cells/18bits = 15,360 18-bit words

- c) FF capacity: 38,400 FF/18bits = 2,133 18-bit words

Wash interval  $\Delta t = ?$  (to be computed ...)

### And the reliability model is defined as follows ...

Now, assume that the probability of an upset in a single bit, after time  $\Delta t$ , can be obtained by using the following relation:

$$P_{1,1} = 1 - e^{-\lambda \Delta t} \tag{I}$$

(where  $e^{-\lambda \Delta t}$  is the survival probability in  $\lambda \Delta t$  days for a single bit)

Assuming that the probability  $P_{1,1}$  is the same for each bit, and the occurrence of an error in a bit is independent of the occurrence of errors in any of the other bits, the probability of r errors in n bits is given by the binomial distribution:

$$P_{r,n} = C_{n,r} \cdot P_{1,1}^{r} \cdot (1 - P_{1,1})^{n-r}$$

(II)

(where  $C_{n,r}$  denotes the number of combinations of r errors in n bits)

Initially, the code word is error free. After time  $\Delta t$ , the probability that the code word is correct is:

$$R_1(\Delta t) = 1 - P_{r,n}$$

$r = d + 1$  (III)

(where d is the number of errors which can always be detected)

After N intervals of  $\Delta t$ , the probability that the code word is correct is:

$$R_1(N\Delta t) = [1 - P_{r,n}]^N$$

(IV)

Assuming independence of the code words, the reliability of a system of W code words after time  $N\Delta t$  is:

$$R_{w}(N\Delta t) = [1 - P_{r,n}]^{NW}$$

(V)

The expected life of the system, which is referred to as mean time before failure (MTBF), is defined by the equation:

$$MTBF = \int_0^\infty R_w dt \quad \text{(where } R_w \text{ is the reliability of the system)}$$

(VI)

Noting that  $N = t/\Delta t$ , then:

$$R_{w}(N\Delta t) = \{[1 - P_{r,n}]^{W/\Delta t}\}^{t}$$

(VII)

which when substituted into (VI), yields the solution:

$$MTBF = \underbrace{-\Delta t}_{VIII}$$

$$WIn[1 - P ]$$

(VIII)

# Thank you for your attention ...